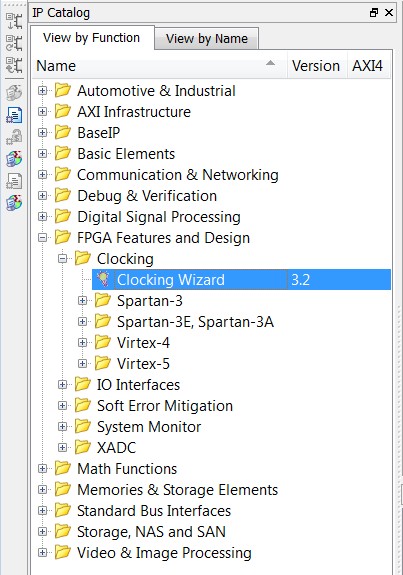

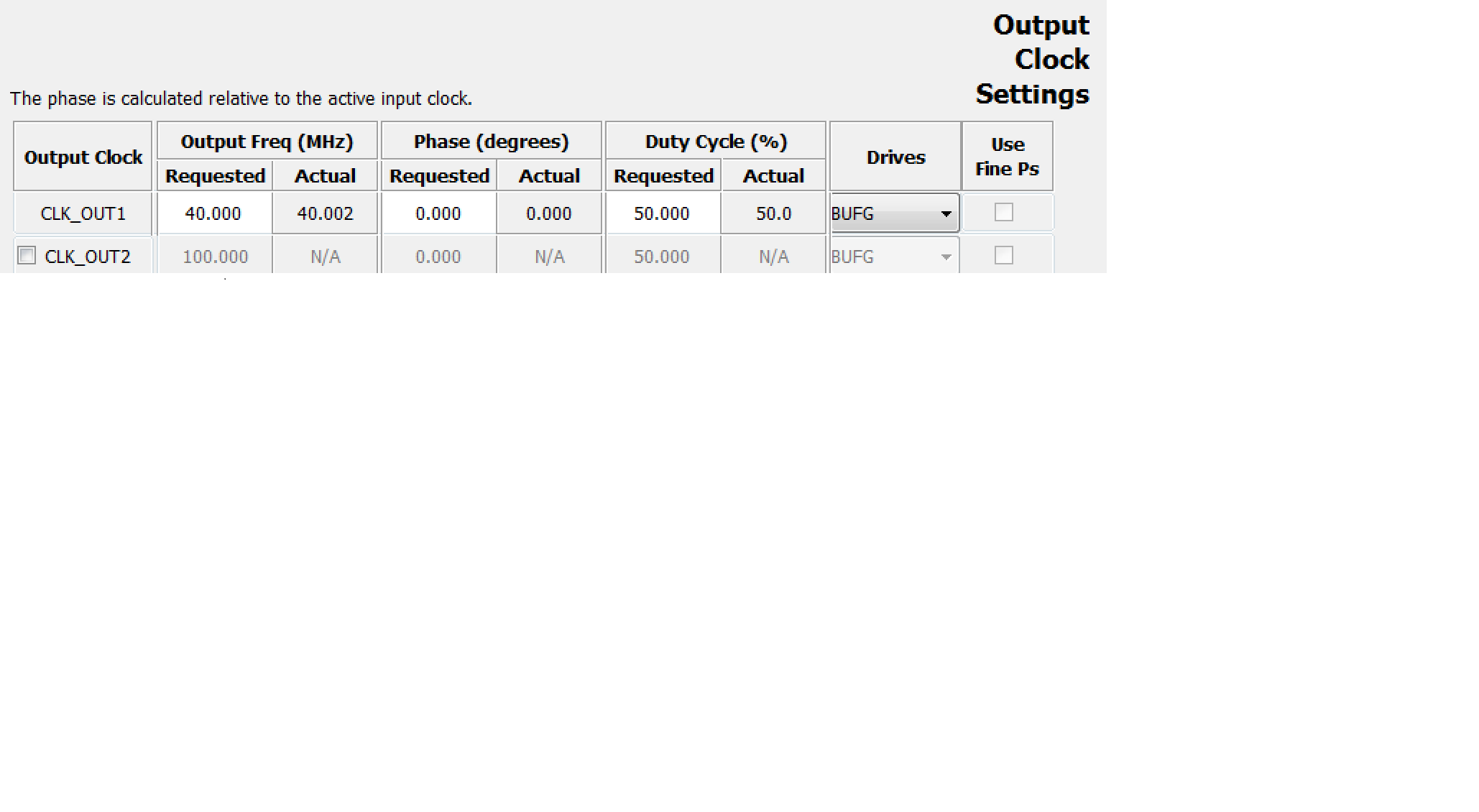

Básicamente, hay dos formas de hacer esto. La primera es usar el núcleo sintetizador de reloj nativo de Xilinx. Una de las ventajas de esto es que las herramientas de Xlinx reconocerán el reloj como tal y lo rutearán a través de las vías requeridas. Las herramientas también manejarán cualquier restricción de tiempo (no realmente aplicable en este caso, ya que es un reloj de 2Hz)

La segunda forma es usar un contador para contar el número de pulsos de reloj más rápidos hasta que haya pasado la mitad de su período de reloj más lento. Por ejemplo, para tu caso, el número de pulsos de reloj rápidos que componen un período de reloj de un ciclo de reloj lento es 50000000/2 = 25000000. Dado que queremos la mitad de un período de reloj, eso es 25000000/2 = 12500000 para cada mitad del ciclo. (la duración de cada alto o bajo).

Así es como se ve en VHDL:

library IEEE;

use IEEE.STD_LOGIC_1164.all;

-- Descomenta la siguiente declaración de la librería si estás usando

-- funciones aritméticas con valores firmados o no firmados

use IEEE.NUMERIC_STD.all;

entity scale_clock is

port (

clk_50Mhz : in std_logic;

rst : in std_logic;

clk_2Hz : out std_logic);

end scale_clock;

architecture Behavioral of scale_clock is

signal prescaler : unsigned(23 downto 0);

signal clk_2Hz_i : std_logic;

begin

gen_clk : process (clk_50Mhz, rst)

begin -- proceso gen_clk

if rst = '1' then

clk_2Hz_i <= '0';

prescaler <= (others => '0');

elsif rising_edge(clk_50Mhz) then -- flanco de reloj ascendente

if prescaler = X"BEBC20" then -- 12 500 000 en hex

prescaler <= (others => '0');

clk_2Hz_i <= not clk_2Hz_i;

else

prescaler <= prescaler + "1";

end if;

end if;

end process gen_clk;

clk_2Hz <= clk_2Hz_i;

end Behavioral;

Detalles a tener en cuenta:

- El reloj generado es cero durante el reset. Esto está bien para algunas aplicaciones y no para otras, solo depende de para qué necesitas el reloj.

- El reloj generado será rutado como una señal normal por las herramientas de síntesis de Xilinx.

- 2Hz es muy lento. Simular durante un segundo va a tomar un tiempo. Es una pequeña cantidad de código, así que debería ser relativamente rápido de simular incluso por 1 segundo, pero si comienzas a agregar código, el tiempo tomado para simular un ciclo de reloj de 2 Hz podría ser significativamente largo.

EDITAR: clk_2Hz_i se utiliza para almacenar en búfer la señal de salida. VHDL no permite usar una señal a la derecha de una asignación cuando también es una salida.

13 votos

Entonces, ¿qué has intentado realmente?

0 votos

¿Por qué no usar Xilinx Clock Manager IP?