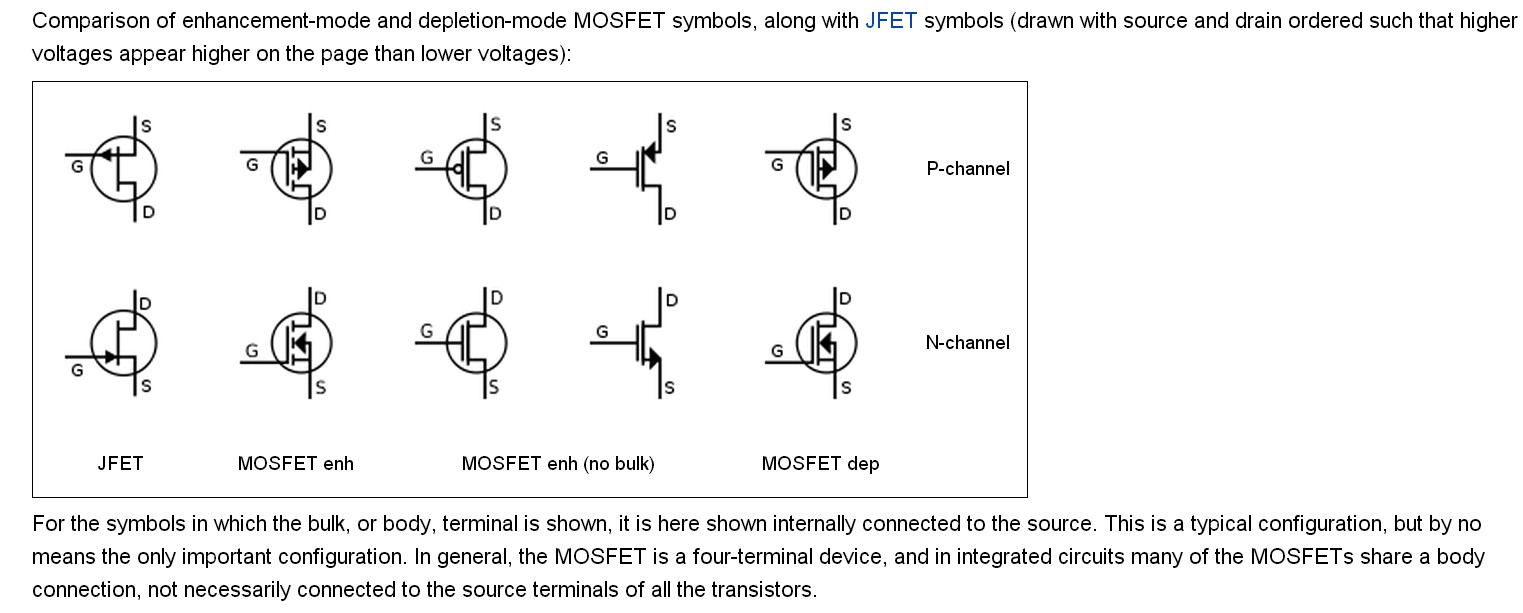

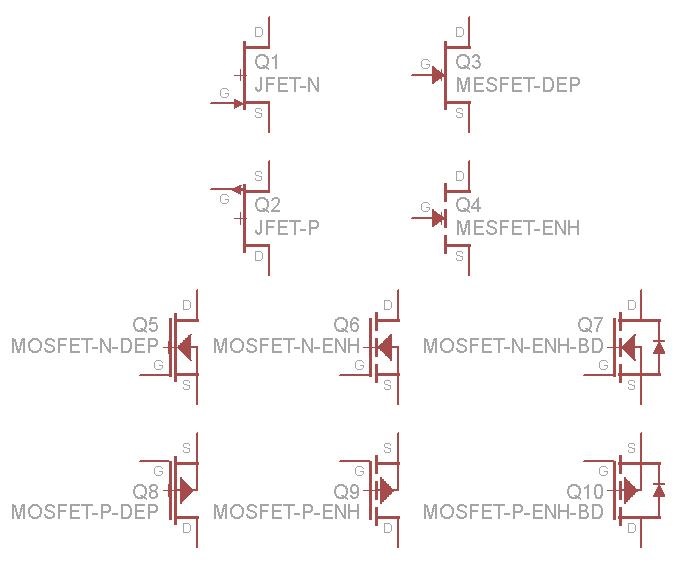

Algunos MOSFETs, incluidos la mayoría de los que se encuentran en paquetes "independientes", tienen la fuente conectada al drenaje. Tales MOSFETs tendrán un diodo inherente en ellos entre la fuente y el drenaje, que conducirá si el MOSFET está polarizado en la dirección opuesta a la dirección en la que normalmente cambiaría (por ejemplo, si la fuente es más positiva que el drenaje para un NFET, o más negativa que el drenaje para un PFET). La flecha en el símbolo indica la polaridad de este diodo.

Otros MOSFETs, especialmente los que se encuentran dentro de chips de lógica digital, tienen los sustratos conectados a un riel de alimentación, independientemente de sus conexiones de fuente, drenaje y compuerta. Aunque se podrían incluir dichas conexiones en un esquemático, hacerlo sería algo así como agregar conexiones de rieles de alimentación a cada compuerta lógica en un esquemático. Dado que el 99% de las compuertas lógicas tienen su VDD conectado a un VDD común y su VSS conectado a un VSS común, tales conexiones serían un ruido visual. De igual manera, cuando el 99% de los NFETs tienen su sustrato conectado al punto más negativo y el 99% de los PFETs tienen su sustrato conectado al punto más positivo. Si la conexión del sustrato de un MOSFET se da por entendida en lugar de verse, se podría distinguir entre NFETs y PFETs usando una flecha para la terminal de sustrato no conectada, pero eso podría ser algo extraño.

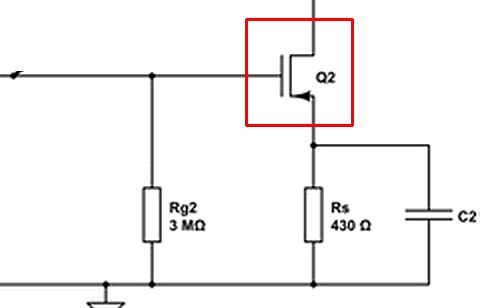

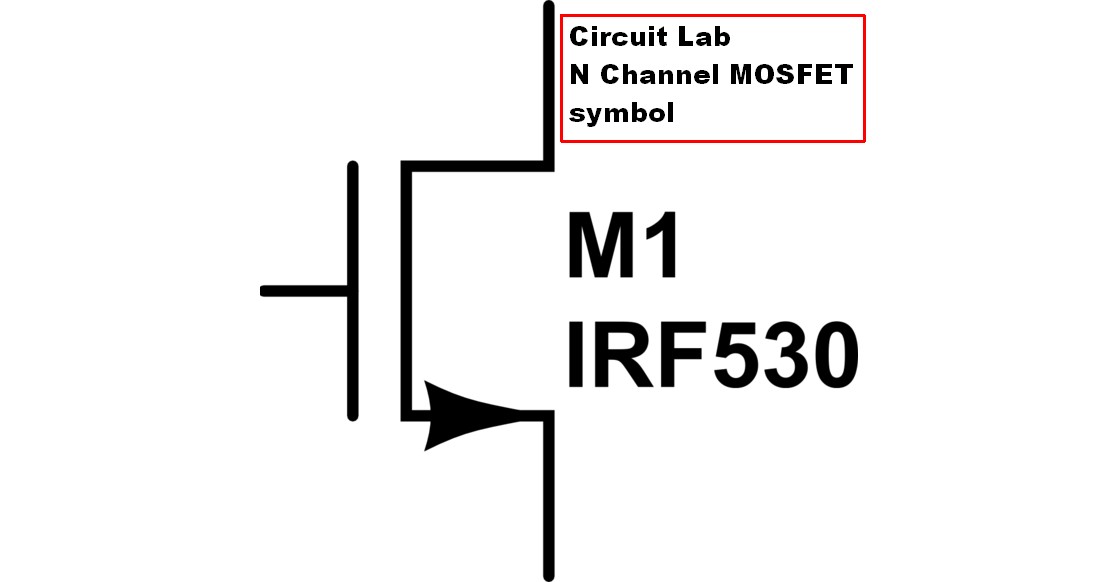

Además, aunque es posible construir un MOSFET cuyo canal fuente-drenaje sea simétrico, el uso de un canal asimétrico mejorará el rendimiento cuando el dispositivo se utiliza para cambiar la corriente en una dirección, a expensas de su rendimiento en la otra dirección. Dado que esto suele ser deseable, suele ser útil tener símbolos esquemáticos que distingan entre la fuente y el drenaje. Dado que el símbolo del sustrato conectado a la fuente "marca" el terminal de la fuente, y dado que los símbolos BJT marcan el emisor cuyo uso más se asemeja a la fuente, es común que los símbolos MOSFET que no tienen un sustrato marcado usen una flecha cuya dirección es análoga a la de un BJT.

Desde mi punto de vista, la forma de apreciar la distinción es darse cuenta de que cuando se muestra una flecha para el sustrato, eso representa un lugar por lo general hay que evitar que circule corriente en la dirección de la flecha, mientras que cuando se muestra una flecha para la fuente, eso representa el flujo de corriente deseado.

Mi preferencia personal es usar un símbolo NFET con una flecha que apunta hacia afuera en la fuente, posiblemente con una flecha de drenaje fuente con polarización inversa en casos en los que sea relevante. Para un PFET, uso una flecha de fuente que apunta hacia adentro, y también añado un círculo en la compuerta. Cuando estoy esbozando diseños VLSI conceptuales con fines ilustrativos (nunca he participado en el diseño de un chip fabricado en realidad), el símbolo NFET y el símbolo FET para transistores utilizados como puertas de paso bidireccionales no tendrán ninguna flecha, pero usarán el círculo o la ausencia del mismo como indicador de polaridad.

Curiosamente, me resulta curioso que en los casos en los que se utilizan MOSFETs discretos para producir puertas de paso, es típico usar dos FETs en sentido contrario, cada uno de los cuales tiene su fuente conectada al sustrato. Puedo entender que en casos en los que un circuito conecte la fuente de un MOSFET a su sustrato, fabricar una parte con ellas conectadas es más barato y más fácil que incluir un aislante; Sin embargo, pensaría que sería más barato fabricar un MOSFET con sustrato aislado que hacer dos MOSFETs cada uno con una conexión fuente-sustrato. Me pregunto si las conexiones individuales fuente-sustrato serían generalmente "preferidas" dentro de un diseño VLSI excepto por el hecho de que es más fácil conectar muchos transistores con un sustrato común que aislar las conexiones de sustrato de transistores que tienen fuentes aisladas. Quizás la situación sea algo análoga a los tubos de vacío (algunos tubos conectan el cátodo a una de las conexiones del filamento, pero otros usan un pin de cátodo separado)?

0 votos

Dudo que obtengas una respuesta objetiva a esta pregunta, ya que hay múltiples opiniones sobre el tema y (que yo sepa) no hay estándares internacionales sobre los símbolos de los componentes. (El hecho de que hayas visto múltiples símbolos aquí debería ser una pista de que 'todo vale'.)

0 votos

Deberías usar el símbolo que sea pertinente. Si realmente estás haciendo hincapié en un dispositivo de mejora, deberías utilizar uno con un canal punteado, por ejemplo. Pero en su mayor parte, no importa realmente.

0 votos

chat.stackexchange.com/transcript/message/9424690#9424690

1 votos

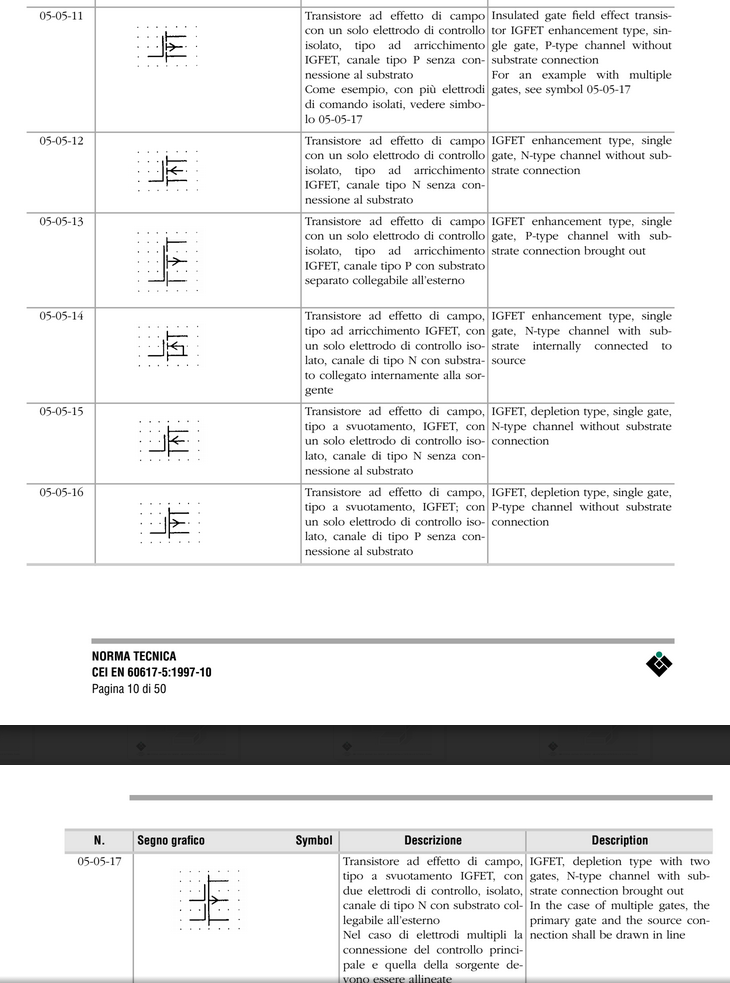

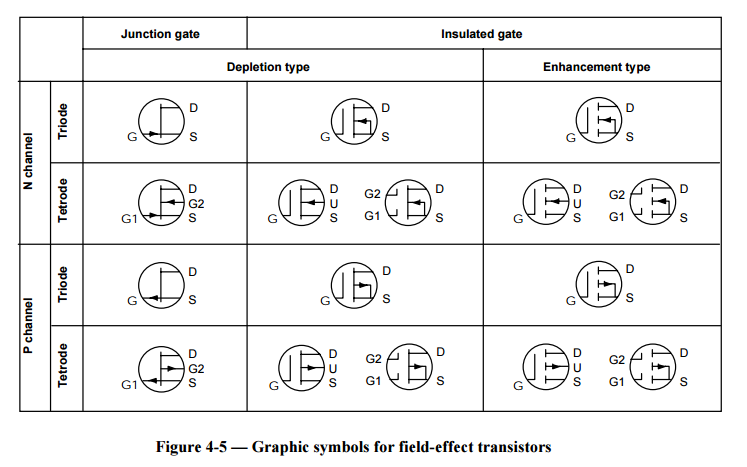

Existe un estándar internacional para estos símbolos, guste o no a alguien. Supongo que a muchos lectores no les gustará. Ver respuesta a continuación.

0 votos

Cuando tengas dudas, elige el símbolo utilizado en la hoja de datos del fabricante.