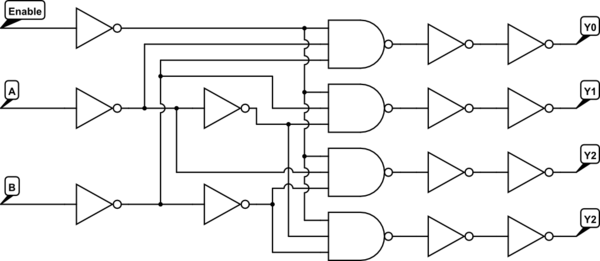

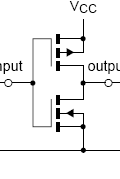

El tiempo requerido para que un gate cambie depende de la cantidad de carga capacitiva que debe conducir, del tamaño de los transistores y del número de transistores en serie. Un inversor consiste en un NFET (transistor de efecto de campo de canal N) y un PFET (FET de canal P); una compuerta NAND de tres entradas tiene tres PFET en paralelo y tres NFET en serie. Para que una compuerta NAND de 3 entradas cambie a bajo rápidamente como lo haría un inversor, cada uno de los tres NFET tendría que ser tres veces más grande que el NFET único de un inversor.

Para un chip pequeño como este, los únicos transistores que tienen que conducir una carga significativa son los conectados a los pines de salida. Usando cuatro salidas conducidas por inversores, será necesario tener cuatro PFET grandes y cuatro NFET grandes, además de un montón de transistores pequeños. Si se asigna un área de "1" a los NFET, los PFET probablemente tendrían un área de aproximadamente 1,5 (el material de canal P no funciona tan bien como el de canal N), para un área total de aproximadamente 10. Si las salidas fueran conducidas directamente por compuertas NAND, sería necesario usar doce PFET grandes (área total 18) y doce enormes NFET (área total 36), para un área total de aproximadamente 54. Al agregar 20 NFET pequeños y 20 PFET pequeños (12 de cada uno para la NAND, y 8 de cada uno para los inversores) el circuito reducirá el área consumida por los transistores grandes en 44 unidades, ¡más del 80%!

Aunque hay ocasiones en las que un pin de salida será conducido directamente por una "puerta lógica" que no sea un inversor, conducir las salidas de esa manera aumenta significativamente el área requerida para los transistores de salida; generalmente solo vale la pena en casos donde, por ejemplo, un dispositivo tiene dos entradas de suministro de energía y debe poder llevar su salida a bajo incluso cuando solo un suministro está funcionando.